Figure 2 from A 3.6 mW, 90 nm CMOS Gated-Vernier Time-to-Digital Converter With an Equivalent Resolution of 3.2 ps | Semantic Scholar

Figure 11 from A Multi-Path Gated Ring Oscillator TDC With First-Order Noise Shaping | Semantic Scholar

Figure 3 from A 14-Bit, 1-ps resolution, two-step ring and 2D Vernier TDC in 130nm CMOS technology | Semantic Scholar

Figure 8 from An area efficient asynchronous gated ring oscillator TDC with minimum GRO stages | Semantic Scholar

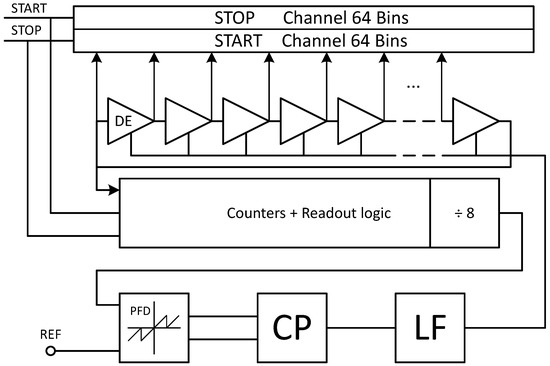

Synthesizable 2D Vernier TDC based on gated ring oscillators Sestavljivi 2D Vernier TDC na osnovi obročnih oscilatorjev

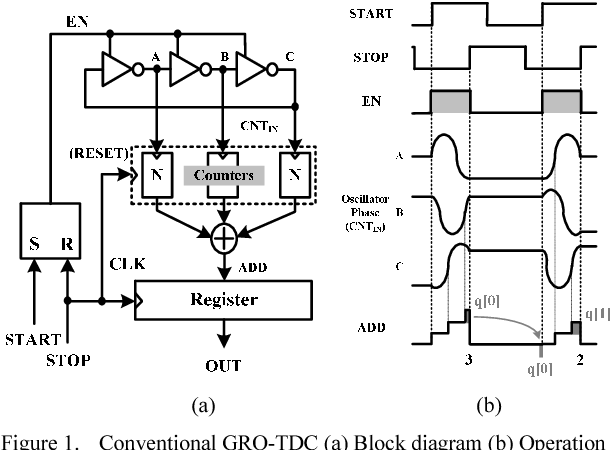

Figure 1 from An area efficient asynchronous gated ring oscillator TDC with minimum GRO stages | Semantic Scholar

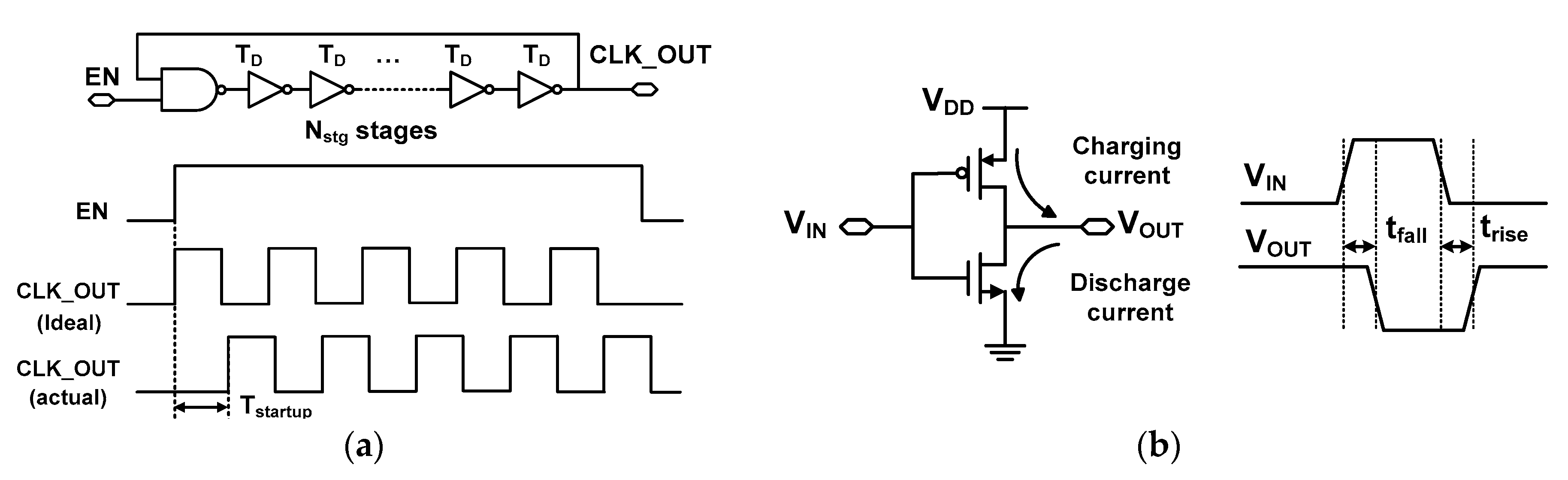

Sensors | Free Full-Text | A Cyclic Vernier Two-Step TDC for High Input Range Time-of-Flight Sensor Using Startup Time Correction Technique

![Gated Ring Oscillator Based TDC [3] | Download Scientific Diagram Gated Ring Oscillator Based TDC [3] | Download Scientific Diagram](https://www.researchgate.net/publication/273163361/figure/fig1/AS:393477943775247@1470823860920/Gated-Ring-Oscillator-Based-TDC-3.png)