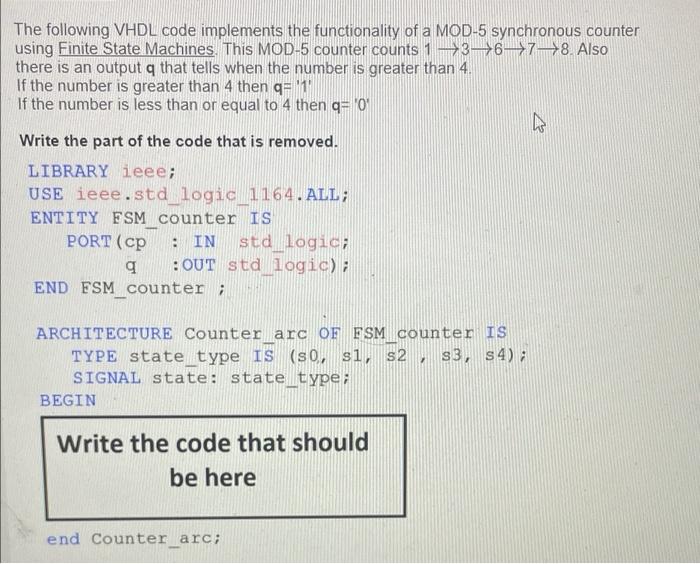

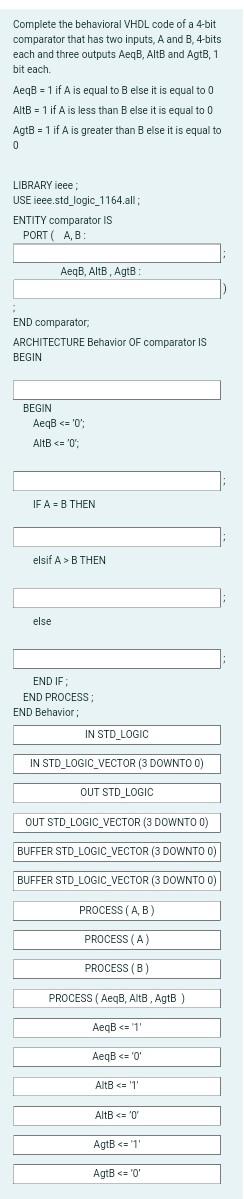

Hardware Design with VHDL VHDL II ECE 443 ECE UNM 1 (9/3/08) RT-Level Combinational Logic This slide set describes Register Tran

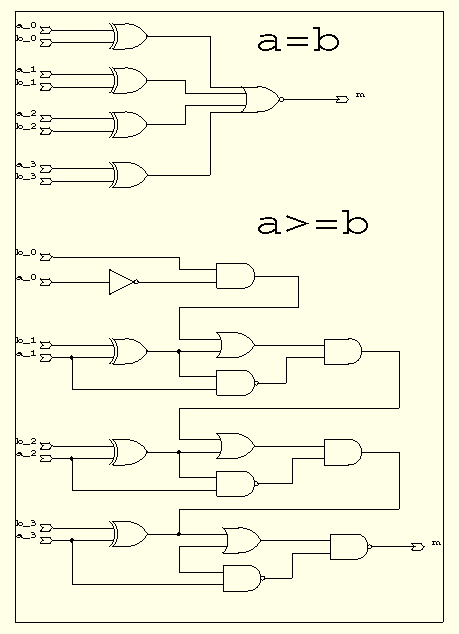

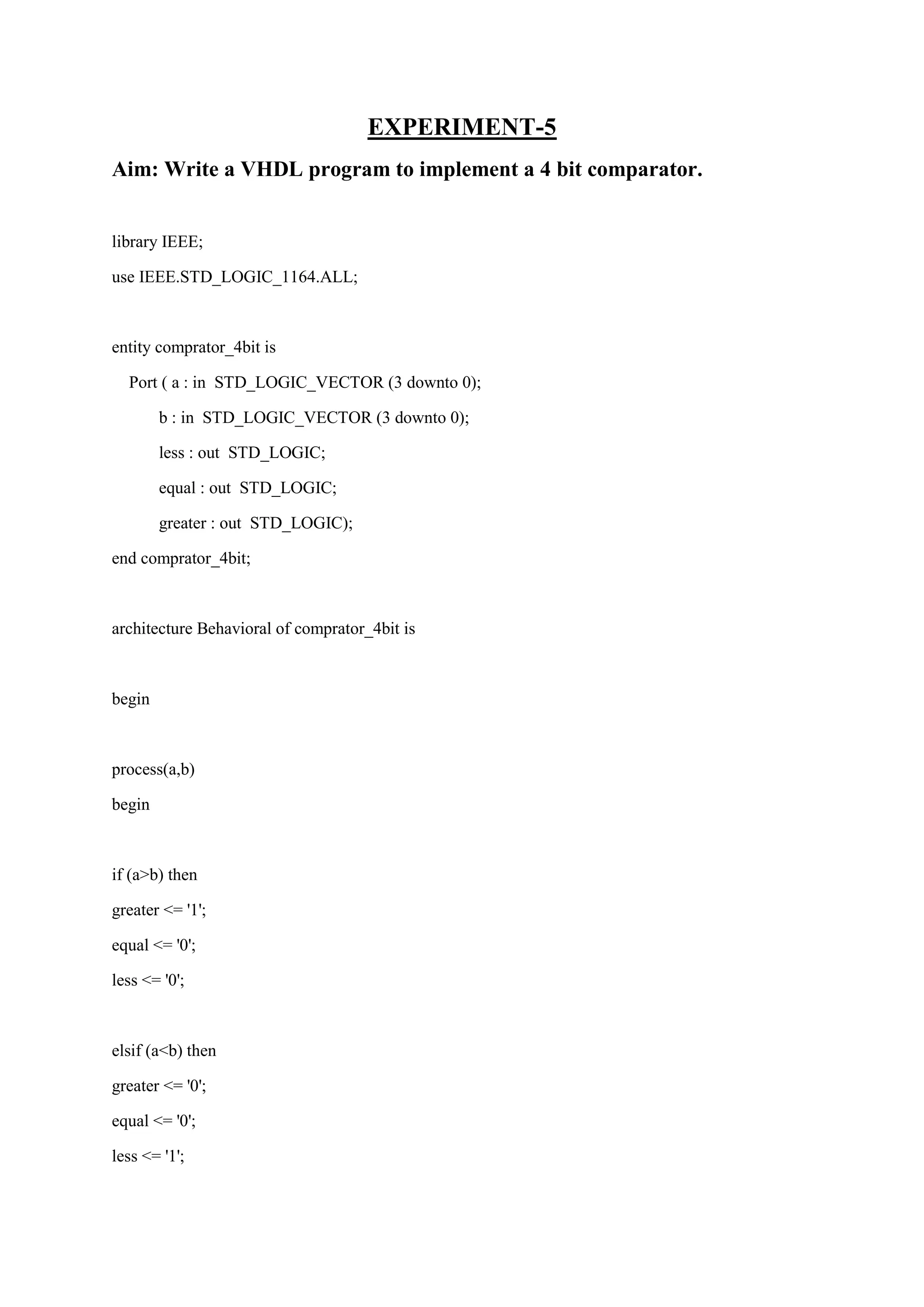

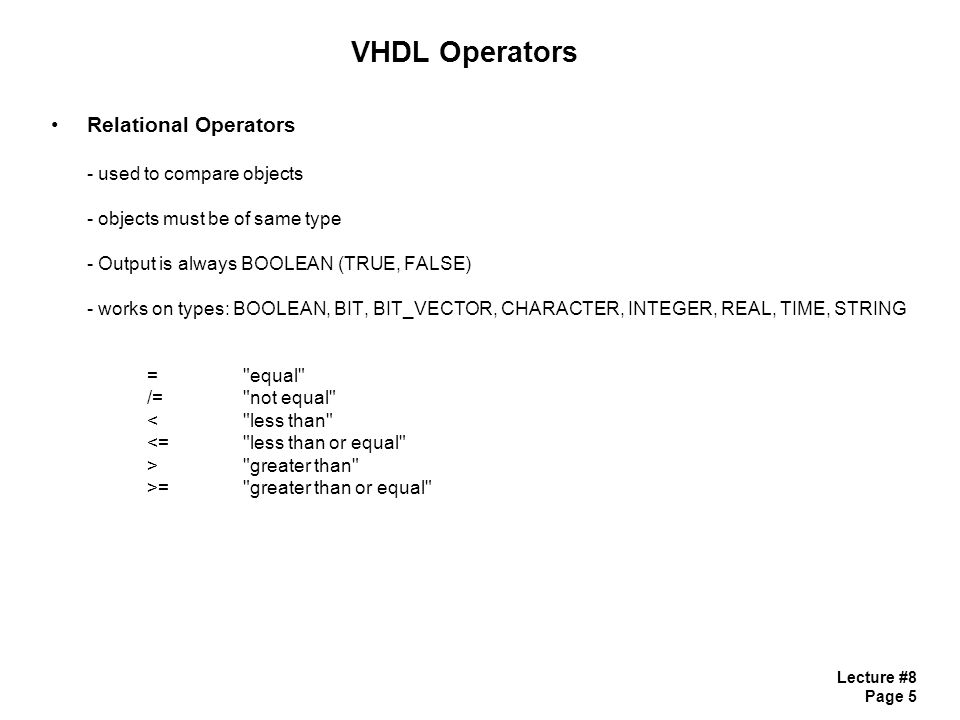

Relational Operators Result is boolean: greater than (>) less than (<) inequality (/=) greater than or equal to (>=) less than or equal to (<=) equal (=) - ppt download

Hardware Design with VHDL VHDL Basics ECE 443 ECE UNM 1 (9/6/12) Skeleton of a Basic VHDL Program This slide set covers the comp

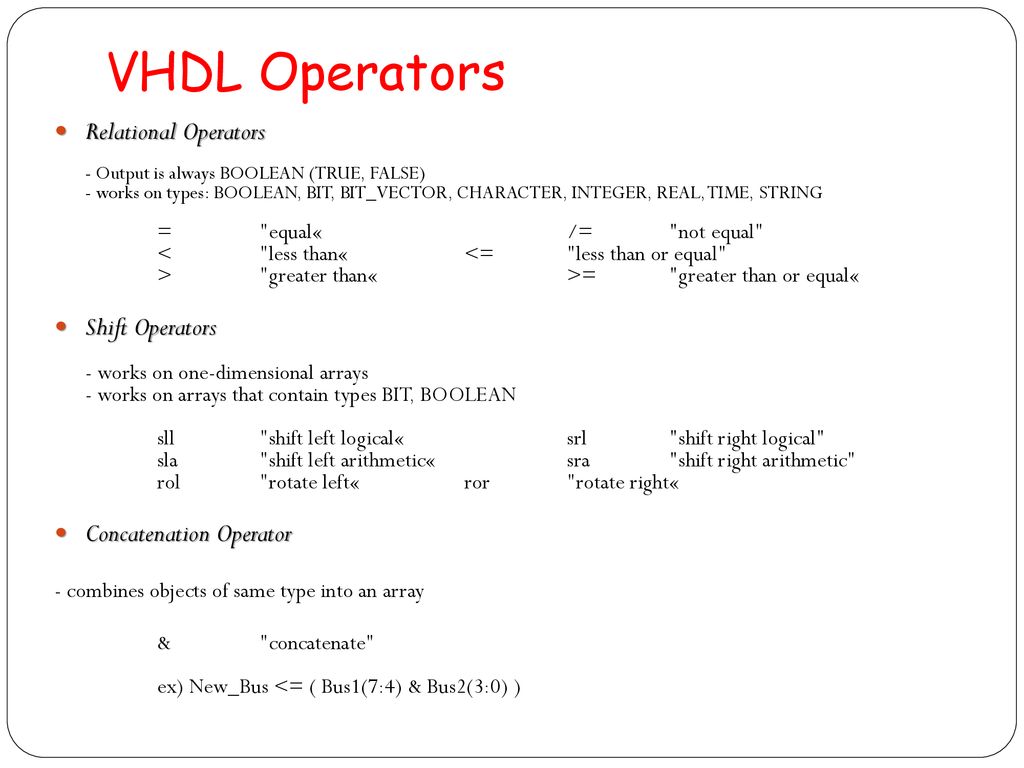

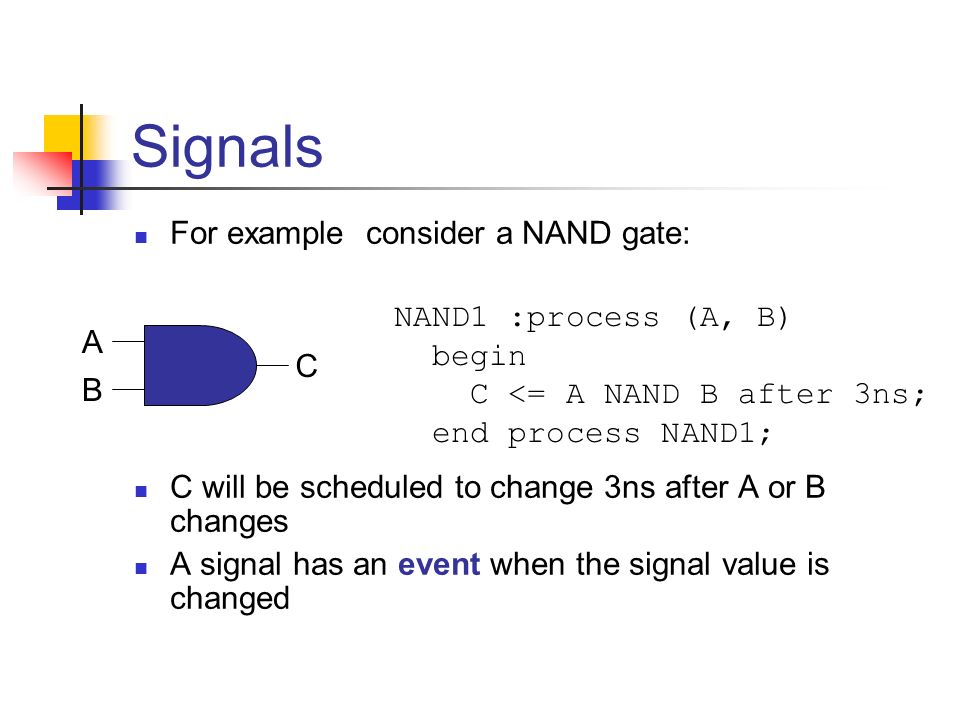

Lecture #8 Page 1 Lecture #8 Agenda 1.VHDL : Operators 2.VHDL : Signal Assignments Announcements 1.HW #4 assigned ECE 4110– Sequential Logic Design. - ppt download

Relational Operators Result is boolean: greater than (>) less than (<) inequality (/=) greater than or equal to (>=) less than or equal to (<=) equal (=) - ppt download

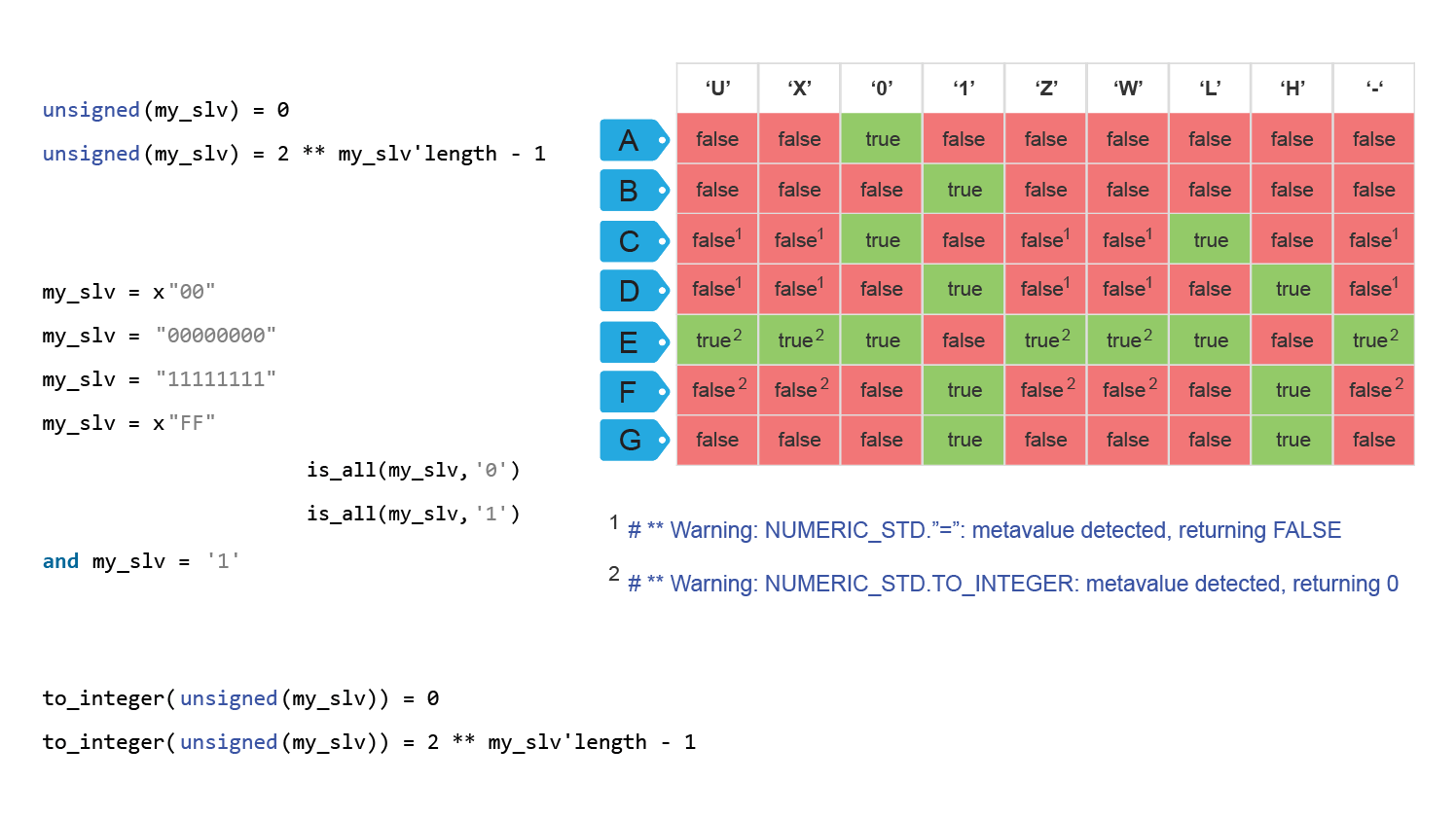

![4.8 VHDL Operators - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book] 4.8 VHDL Operators - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book]](https://www.oreilly.com/api/v2/epubs/9780470900550/files/images/ch004-f017.jpg)